|

1.Spec

¿Ãπ¯ø°¥¬ ¿¸¿⁄≈∞∏¶ º≥∞Ë«œ∞Ì¿⁄ «’¥œ¥Ÿ.

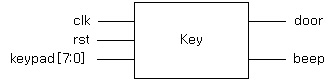

¿Ã ¿¸¿⁄≈∞¥¬ 8∞≥¿« keypad∏¶ ∞°¡ˆ∞Ì ¿÷∞Ì, √‚∑¬¿∏∑Œ beep∞˙ door∞° ¿÷Ω¿¥œ¥Ÿ.

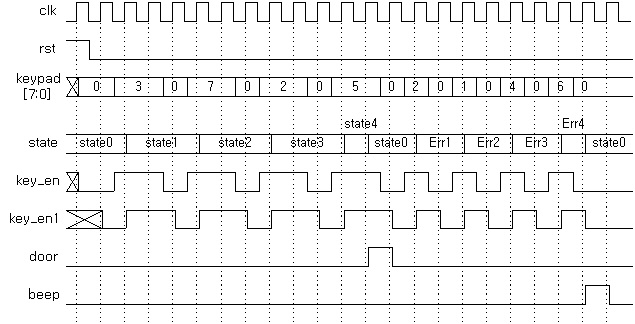

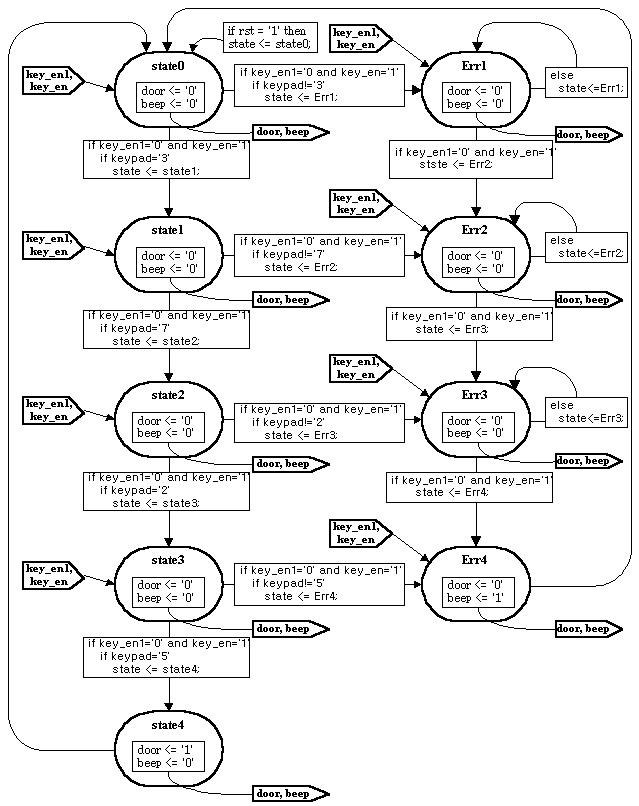

¿¸¿⁄≈∞¿« πÆ¿ª ø≠∑¡∏È 3->7->2->5π¯ º¯¿∏∑Œ keypad ¿‘∑¬¿ª πÞæ∆æþ «’¥œ¥Ÿ.

¿Ã º¯º≠∑Œ ¿‘∑¬µ«∏È door='1'¿Ãµ«æÓ πÆ¿Ã ø≠∏Æ∞Ì, ¿‘∑¬º¯º≠∞° ¿ÃøÕ ¥Ÿ∏£∏È door='0'¿ª ¿Ø¡ˆ«œ∞Ì,

beep='1'¿Ã µ«æÓ ∞Ê∞Ì¿Ω¿Ã øÔ∏∞¥Ÿ∞Ì ∞°¡§«’¥œ¥Ÿ.

¿‘∑¬¥Î±‚ ªÛ≈¬¿Œ state0ø°º≠ state1->state2->state3->state4∑Œ ∞°∏Á,

state4ø°º≠ door='1'¿Ã µÀ¥œ¥Ÿ.

±◊∑Ø≥™ ¿‘∑¬º¯º≠∞° ∏¬¡ˆ æ ¿ª∞ÊøÏ errorªÛ≈¬∑Œ ∞°¥¬µ• ¿Ã ∂ßø°µµ 4∞≥¿« keypad ¿‘∑¬¿Ã ¿÷æÓæþ∏∏

beep='1'¿Ã µ«∞‘ «œø¥Ω¿¥œ¥Ÿ.

¿Ã ∂ß ¿Ø»ø«— key¿‘∑¬¿ª πÞæ∆µÈ¿Ã±‚ ¿ß«ÿ key_en, key_en1 signal¿ª ¿ÃøΫœø©

key¿‘∑¬ ªÛΩ¬ø©∫Œ∏¶ check«œµµ∑œ º≥∞Ë«œø¥Ω¿¥œ¥Ÿ.

2,Input/Output

3.Timing

4.Block Diagram

5.VHDL Code : key.vhd

Test Vector : key_tb.vhd

|

|